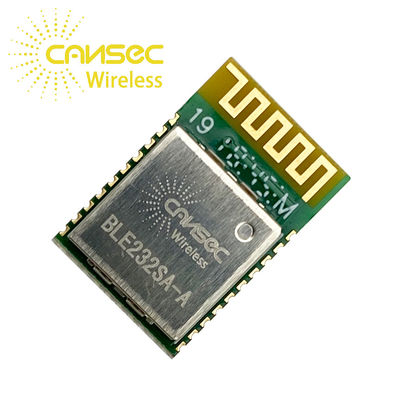

Niederleistungs-drahtloses Ble232SA-A drahtloses Modul St. Bluenrg-2 der Bluetooth-Modul-niedrigen Kosten-

Preiswertes drahtloses Ble232SA-A drahtloses Modul St. Bluenrg-2 Niederleistungs-Bluetooth-Modul-

Beschreibung

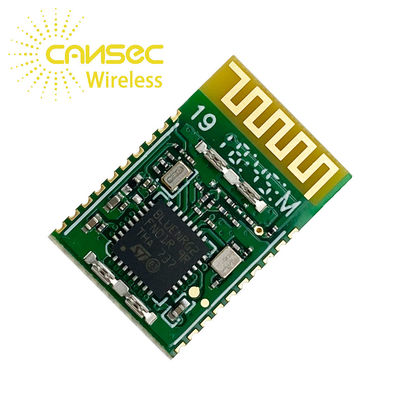

BLE232SA-/UAreihenmodul ist basiert auf dem BlueNRG-2 St.-Firma entworfen. Das BlueNRG-2 ist ein Monomode--System-aufchip niedriger Energie Bluetooths der geringen Energie (BLE5.0), der mit Bluetooth-Spezifikation konform ist.

Das BlueNRG-2 verlängert die Eigenschaften des award-winningbluenrg-intelligenten Knotens und ermöglicht der Verwendung der eingebetteten Rinde M0 für laufenden Benutzeranwendungscode.

Das BlueNRG-2 schließt 256kB des Programmierungsflash-speichers, 24 KB statisches RAM-Gedächtnisses mit Zurückhalten (zwei Banken 12kB) und des SPIs, UART, I2C-Standardkommunikationsschnittstellenperipherie mit ein. Es kennzeichnet auch Multifunktionstimer, Wachhund, RTC- und DMA-Controller.

Eine ADC ist für die Zusammenschaltung an analoge Sensoren und für das Ablesen des Maßes des integrierten Batteriemonitors verfügbar. Ein digitaler Filter ist für die Verarbeitung von PDM-Strom verfügbar.

Das BlueNRG-2 bietet die gleiche ausgezeichnete Rf-Leistung als der BlueNRG-Radio an, und der integrierte Konverter der Hochleistungsfähigkeit DC/DC hält die gleichen ultra-niedrigen Energieeigenschaften, aber das BlueNRG-2 verbessert die Stromaufnahme des BlueNRG-Schlafmodus, eine weiterere Zunahme der Batterielebenszeit der Anwendungen erlaubend.

Anwendungen

- Uhren

- Eignung, Wellness und Sport

- Verbraucher medizinisch

- Sicherheit/Nähe

- Fernbedienung

- Haupt- und industrielle Automatisierung

- Betreutes Wohnen

- Handyperipherie

- Beleuchten von PC peripher

Eigenschaften

- Monomode--System-aufchip niedriger Energie Bluetooths konform mit Bluetooth 5,0 Spezifikationen:

Meister-, Sklaven- und mehrfachesimultane Rollen

Le-Datenpaket-Längenerweiterung

- Betriebsstoffspannung: von 1,7 bis 3,6 V

- Integrierter linearer Regler und DC-DC Abwärtskonverter

- Betriebstemperaturbereich:

-30 °C zu °C 85

- Leistungsstark, basierter Architektur32-bit-kern Ultra-niedrigenergie Rinde M0

- Programmierbarer 256 KB Blitz

- 24 KB RAM mit Zurückhalten (zwei 12 KBbanken)

- 1 Schnittstelle x UART

- 1 Schnittstelle x SPI

- 2 x I ² C Schnittstelle

- 15GPIOs

- Multifunktionstimer mit 2 x

- ADC 10-bit

- Wachhund und RTC

- DMA-Controller

- PDM-Stromprozessor

- 32-MHZ-Quarzoszillator

- 32-kHz-Quarzoszillator

- Batterie-Spg. Kontrollempfänger und Temperaturfühler

(am Antennenverbindungsstück)

- Ausgezeichnetes Rf-Verbindungsbudget (DB bis 96)

- Genaues RSSI, zum der Sendeleistung zu erlauben

8,3 MA TX gegenwärtig (@ -2 dBm, 3,0 V)

- Unten zu 1 µA Stromaufnahme mit aktivem BLE-Stapel (Schlafmodus)

- Stromaufnahme der durchschnittlichen Anzeige

µA 15,34 (Anzeigenabstand1000 Frau), 1-jährig, 8 Monate, 19 Tage mit 230 Milliamperestunden-Batterie (CR2032)

- Stromaufnahme der durchschnittlichen Verbindung

µA 7,059 (Verbindungsabstand1000 Frau), 3 Jahre, 10 Monate, 12 Tage mit 230mAhbattery (CR2032)

- Passend für die errichtenden Anwendungen konform mit den folgenden Hochfrequenzregelungen: ETSI-en 300 328, en 300 440, Teil 15, ARIB STD-T66 FCC CFR47

- Vorprogrammiertes Urladeprogramm über UART

- Bis +8 dBm verfügbare Spitzenleistung

Anmerkung A: ll Eigenschaften von BLE5.0 werden nicht z.Z. gestützt, aber es ist der meiste Kostenverlaufchip zur Unterstützung BLE5.0.

Ihre Nachricht muss zwischen 20 und 3.000 Zeichen enthalten!

Ihre Nachricht muss zwischen 20 und 3.000 Zeichen enthalten! Bitte überprüfen Sie Ihre E-Mail!

Bitte überprüfen Sie Ihre E-Mail!  Ihre Nachricht muss zwischen 20 und 3.000 Zeichen enthalten!

Ihre Nachricht muss zwischen 20 und 3.000 Zeichen enthalten! Bitte überprüfen Sie Ihre E-Mail!

Bitte überprüfen Sie Ihre E-Mail!